# CA3059, CA3079

Oct 1999

# Features

- Relay Control

- Valve Control

- Synchronous Switching of Flashing Lights

- · On-Off Motor Switching

intersi

Differential Comparator with Self-Contained Power Supply for Industrial Applications

OBSOLETE PRODUCT NO RECOMMENDED REPLACEMENT

our Technical Support Center at our recinical suppor Center at 1-888-INTERSIL or www.intersil.com/tsc

- Photosensitive Control

- Power One-Shot Control

- Heater Control

- Lamp Control

## Type Features

| Type Features                                                                 | CA3059  | CA3079 |

|-------------------------------------------------------------------------------|---------|--------|

| <ul> <li>24V, 120V, 208/230V, 277V at 50/60<br/>or 400Hz Operation</li> </ul> | Х       | Х      |

| Differential Input                                                            | Х       | Х      |

| + Low Balance Input Current (Max) - $\mu \textbf{A}.$                         | 1       | 2      |

| Built-In Protection Circuit for Opened or Shorted Sensor (Term 14)            | X       | Х      |

| • Sensor Range (Rx) - kΩ                                                      | 2 - 100 | 2 - 50 |

| • DC Mode (Term 12)                                                           | Х       |        |

| External Trigger (Term 6)                                                     | Х       |        |

| External Inhibit (Term 1)                                                     | х       |        |

| DC Supply Volts (Max)                                                         | 14      | 10     |

| • Operating Temperature Range (°C)                                            | -55 to  | +125   |

# Ordering Information

|             | -               |                     |

|-------------|-----------------|---------------------|

| PART NUMBER | TEMPERATURE     | PACKAGE             |

| CA3059      | -55°C to +125°C | 14 Lead Plastic DIP |

| CA3079      | -55°C to +125°C | 14 Lead Plastic DIP |

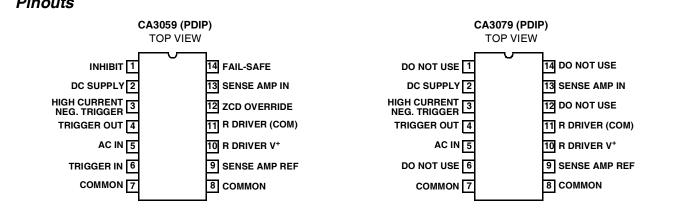

# Pinouts

# Zero-Voltage Switches for 50Hz-60Hz and 400Hz Thyristor Control Applications

# Description

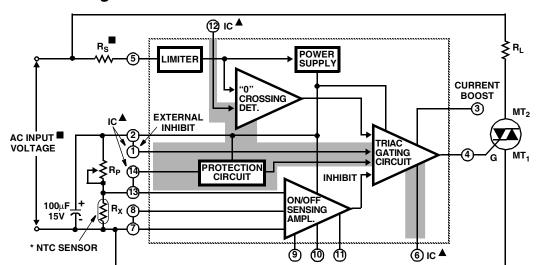

The CA3059 and CA3079 zero-voltage switches are monolithic silicon integrated circuits designed to control a thyristor in a variety of AC power switching applications for AC input voltages of 24V, 120V, 208/230V, and 277V at 50Hz-60Hz and 400Hz. Each of the zero-voltage switches incorporates 4 functional blocks (see the Functional Block Diagram) as follows:

- 1. Limiter-Power Supply Permits operation directly from an AC line.

- 2. Differential On/Off Sensing Amplifier Tests the condition of external sensors or command signals. Hysteresis or proportional-control capability may easily be implemented in this section.

- 3. Zero-Crossing Detector Synchronizes the output pulses of the circuit at the time when the AC cycle is at zero voltage point; thereby eliminating radio-frequency interference (RFI) when used with resistive loads.

- 4. Triac Gating Circuit Provides high-current pulses to the gate of the power controlling thyristor.

In addition, the CA3059 provides the following important auxiliary functions (see the Functional Block Diagram).

- 1. A built-in protection circuit that may be actuated to remove drive from the triac if the sensor opens or shorts.

- 2. Thyristor firing may be inhibited through the action of an internal diode gate connected to Terminal 1.

- 3. High-power dc comparator operation is provided by overriding the action of the zero-crossing detector. This is accomplished by connecting Terminal 12 to Terminal 7. Gate current to the thyristor is continuous when Terminal 13 is positive with respect to Terminal 9.

The CA3059 and CA3079 are supplied in 14 lead dual-inline plastic packages.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a trademark of Intersil Americas Inc. Copyright © Intersil Americas Inc. 2002. All Rights Reserved

# Functional Block Diagram

\* NEGATIVE TEMPERATURE COEFFICIENT

| AC INPUT VOLTAGE (50/60 OR 400Hz)<br>V AC | INPUT SERIES RESISTOR (R <sub>S</sub> )<br>kΩ | DISSIPATION RATING FOR R <sub>S</sub><br>W |

|-------------------------------------------|-----------------------------------------------|--------------------------------------------|

| 24                                        | 2                                             | 0.5                                        |

| 120                                       | 10                                            | 2                                          |

| 208/230                                   | 20                                            | 4                                          |

| 277                                       | 25                                            | 5                                          |

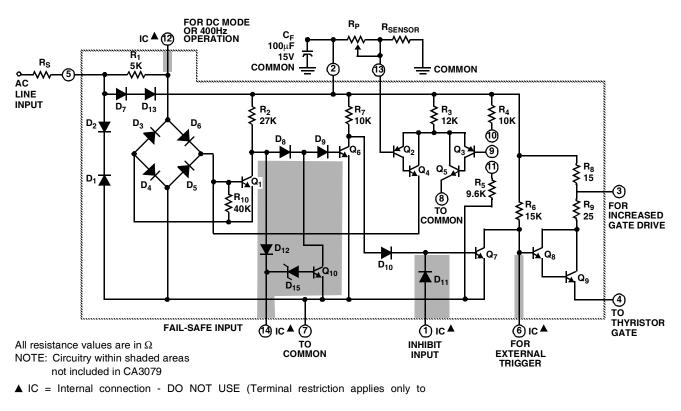

NOTE: Circuitry within shaded areas, not included in CA3079

See chart

▲ IC = Internal connection - DO NOT USE (Terminal restriction applies only to CA3079)

FIGURE 1. SCHEMATIC DIAGRAM OF CA3059 AND CA3079

## Absolute Maximum Ratings T<sub>A</sub> = +25°C

| DC Supply Voltage (Between Terminals 2 & 7) |   |

|---------------------------------------------|---|

| CA3059                                      | ļ |

| CA3079                                      | / |

| DC Supply Voltage (Between Terminals 2 & 8) |   |

| CA3059                                      | ļ |

| CA3079                                      | / |

| Peak Supply Current (Terminals 5 & 7)±50mA  | ۱ |

| Output Pulse Current (Terminal 4) 150mA     | ١ |

|                                             |   |

### **Thermal Information**

| PDIP Package 100                                                | JA<br>°C/W |

|-----------------------------------------------------------------|------------|

| Power Dissipation                                               |            |

| Up to T <sub>A</sub> = +55°C CA3059, CA3079                     | 60mW       |

| Above T <sub>A</sub> = +55°C CA3059, CA3079 Derate Linearly 10m | IW/⁰C      |

| Ambient Temperature                                             |            |

| Operating55°C to +1                                             | 25°C       |

| Storage65°C to +1                                               | 50°C       |

| Lead Temperature (During Soldering)+2                           | 265°C      |

| At distance 1/16" $\pm$ 1/32" (1.59 $\pm$ 0.79) from case       |            |

| for 10 seconds max                                              |            |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

## **Electrical Specifications**

$T_A = +25^{\circ}C$ , For all Types, Unless Otherwise Specified. All voltages are measured with respect to Terminal 7. For Operating at 120V<sub>RMS</sub>, 50-60Hz (AC Line Voltage) (Note 1)

| PARAMETERS                                      |                         | SYMBOL                         | TEST CONDITIONS                                                    | MIN   | ТҮР         | МАХ   | UNITS |  |

|-------------------------------------------------|-------------------------|--------------------------------|--------------------------------------------------------------------|-------|-------------|-------|-------|--|

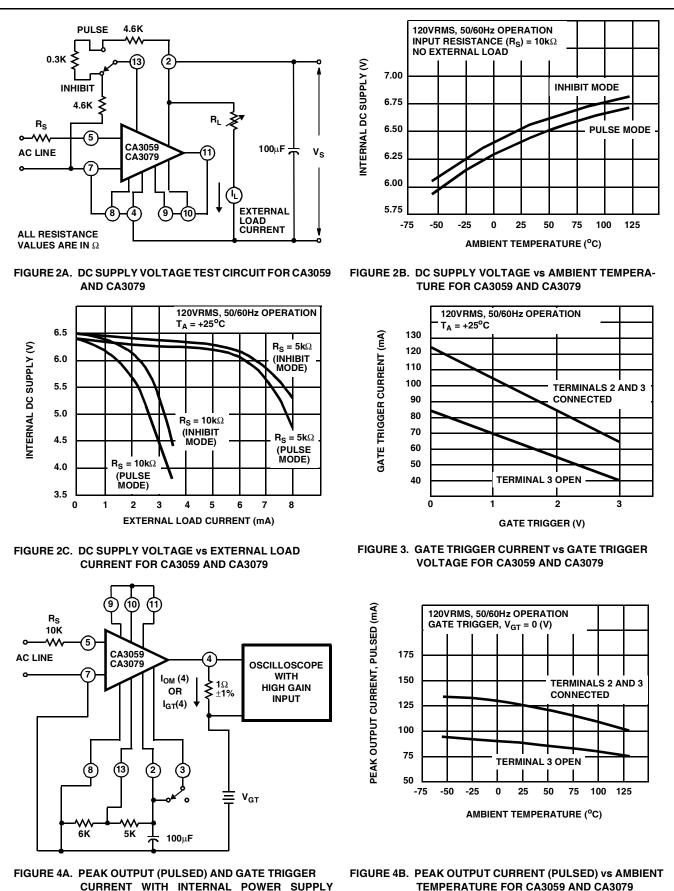

| DC SUPPLY VOLT                                  | AGE (Figure 2A, 2B, 2C) |                                |                                                                    |       |             |       |       |  |

| Inhibit Mode At 50/60Hz                         |                         | V <sub>S</sub>                 | $R_{S} = 8k\Omega, I_{L} = 0$                                      |       | 6.5         | 7     | V     |  |

|                                                 | At 400Hz                |                                | $R_{S} = 10k\Omega, I_{L} = 0$                                     | -     | 6.8         | -     | V     |  |

|                                                 | At 50/60Hz              |                                | $R_{S} = 5k\Omega, I_{L} = 0$                                      | -     | 6.4         | -     | V     |  |

| Pulse Mode At 50/60Hz                           |                         | V <sub>S</sub>                 | $R_{S} = 8k\Omega, I_{L} = 0$                                      | 6     | 6.4         | 7     | V     |  |

|                                                 | At 400Hz<br>At 50/60Hz  |                                | $R_{S} = 10k\Omega, I_{L} = 0$                                     | -     | 6.7         | -     | V     |  |

|                                                 | At 50/60Hz              |                                | $R_{S} = 5k\Omega, I_{L} = 0$                                      | -     | 6.3         | -     | V     |  |

| Gate Trigger Curren                             | t (Figures 3, 4A)       | I <sub>GT</sub><br>Terminal 4  | Terminals 3 and 2 Connected, $V_{GT} = 1V$                         | -     | 105         | -     | mA    |  |

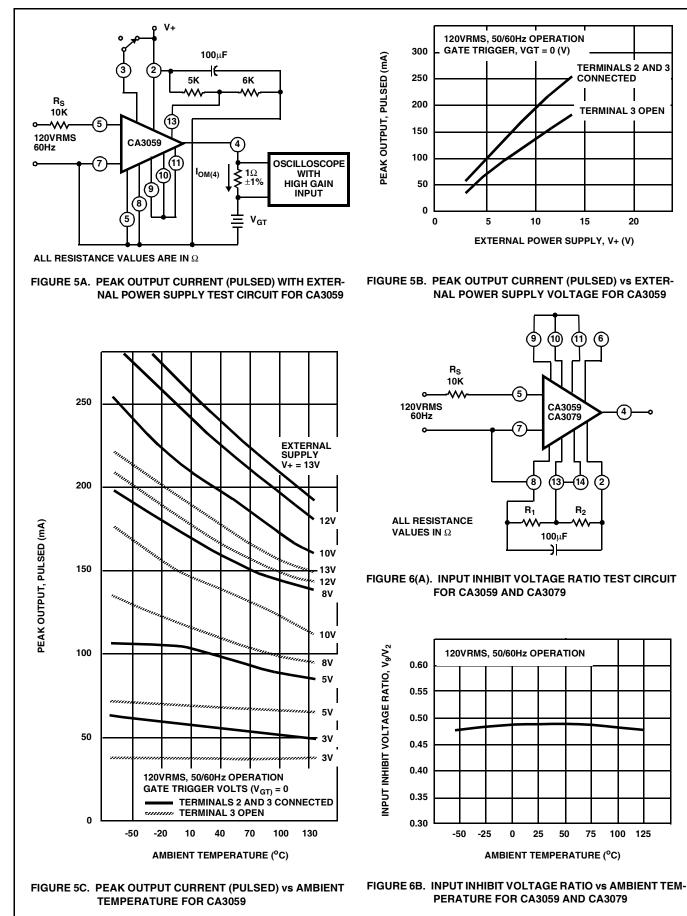

| PEAK OUTPUT CU                                  | RRENT (PULSED) (Figu    | res 4, 5)                      | •                                                                  |       |             |       |       |  |

| With Internal Power Supply<br>Figure 4a, 4b     |                         | I <sub>OM</sub><br>Terminal 4  | Terminal 3 open, Gate Trigger<br>Voltage (V <sub>GT</sub> ) = 0    | 50    | 84          | -     | mA    |  |

|                                                 |                         |                                | Terminals 3 and 2 Connected, Gate Trigger Voltage ( $V_{GT}$ ) = 0 | 90    | 124         | -     | mA    |  |

| With External Power Supply<br>Figure 5a, 5b, 5c |                         | I <sub>OM</sub>                | Terminal 3 open, V+ = 12V, $V_{GT} = 0$                            | -     | 170         | -     | mA    |  |

|                                                 |                         | Terminal 4                     | Terminals 3 and 2 Connected, $V_{+} = 12V$ , $V_{GT} = 0$          |       | 240         | -     | mA    |  |

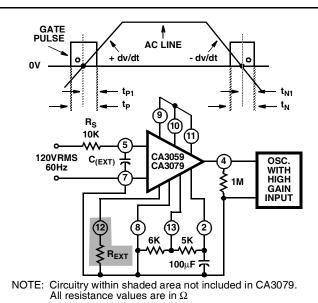

| Inhibit Input Ratio (Figure 6)                  |                         | V <sub>9</sub> /V <sub>2</sub> | Voltage Ratio of Terminals 9 to 2                                  | 0.465 | 0.485       | 0.520 | -     |  |

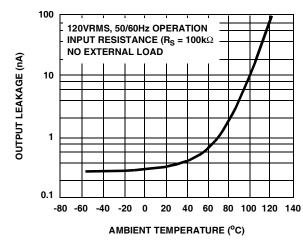

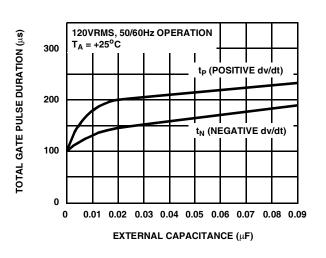

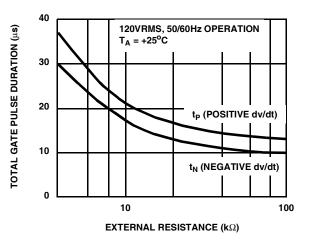

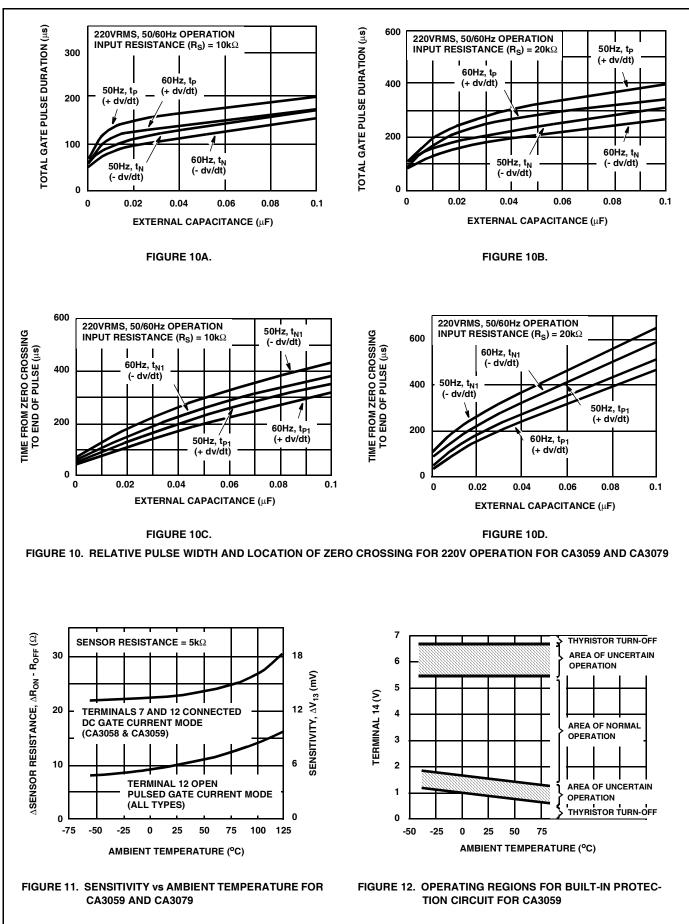

| TOTAL GATE PULS                                 | E DURATION (Note 2) (   | Figure 7A, 7B, 7C              | , 7D)                                                              |       |             |       |       |  |

| For Positive dv/dt                              | 50-60Hz                 | t <sub>P</sub>                 | C <sub>EXT</sub> = 0                                               | 70    | 100         | 140   | μs    |  |

|                                                 | 400Hz                   |                                | $C_{EXT} = 0, R_{EXT} = \infty$                                    | -     | 12          | -     | μs    |  |

| For Negative dv/dt                              | 50-60Hz                 | t <sub>N</sub>                 | C <sub>EXT</sub> = 0                                               | 70    | 100         | 140   | μs    |  |

|                                                 | 400Hz                   |                                | $C_{EXT} = 0, R_{EXT} = \infty$                                    | -     | 10          | -     | μs    |  |

| PULSE DURATION                                  | AFTER ZERO CROSSIN      | NG (50-60Hz) (Fig              | ure 7A)                                                            |       |             |       |       |  |

| For Positive dv/dt                              |                         | t <sub>P1</sub>                | $C_{EXT} = 0, R_{EXT} = \infty$                                    |       | 50          | -     | μs    |  |

| For Negative dv/dt                              |                         | t <sub>N1</sub>                | 1                                                                  | -     | 60          | -     | μs    |  |

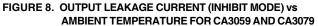

| OUTPUT LEAKAGE                                  | CURRENT (Figure 8)      |                                |                                                                    |       |             |       |       |  |

| Inhibit Mode                                    |                         | I <sub>4</sub>                 |                                                                    | -     | 0.001       | 10    | μA    |  |

| INPUT BIAS CURR                                 | ENT (Figure 9)          | <u>.</u>                       | •                                                                  | •     |             | •     |       |  |

| CA3059                                          |                         | l <sub>l</sub>                 |                                                                    | -     | 220         | 1000  | nA    |  |

| CA3079                                          |                         |                                |                                                                    | -     | 220         | 2000  | nA    |  |

| Common-mode Inpu                                | ut Voltage Range        | V <sub>CMR</sub>               | Terminals 9 and 13 Connected                                       | -     | 1.5 to<br>5 | -     | V     |  |

**Electrical Specifications**  $T_A = +25$

$T_A = +25^{\circ}C$ , For all Types, Unless Otherwise Specified. All voltages are measured with respect to Terminal 7. For Operating at 120V<sub>RMS</sub>, 50-60Hz (AC Line Voltage) (Note 1) **(Continued)**

| PARAMETERS                              | SYMBOL          | TEST CONDITIONS  | MIN | ТҮР | MAX | UNITS |

|-----------------------------------------|-----------------|------------------|-----|-----|-----|-------|

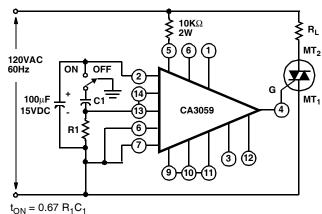

| SENSITIVITY (Note 3) (Figures 4(a), 11) |                 |                  |     |     |     |       |

| Pulse Mode                              | $\Delta V_{13}$ | Terminal 12 open | -   | 6   | -   | mV    |

NOTES:

The values given in the Electrical Characteristics Chart at 120V also apply for operation at input voltages of 208/230V, and 277V, except for Pulse Duration. However, the series resistor (R<sub>S</sub>) must have the indicated value, shown in the chart in the Functional Block Diagram, for the specified input voltage.

2. Pulse Duration in 50Hz applications is approximately 15% longer than shown in Figure 7(b).

3. Required voltage change at Terminal 13 to either turn OFF the triac when ON or turn ON the triac when OFF.

### **Maximum Voltage Ratings** $T_A = +25^{\circ}C$

|              |             |        |          | МА       | AXIMUM      |                    | GE RAT             | TINGS T            |          | °C       |          |                     |          |                            | MAXI<br>CURF<br>RATI  | RENT                   |

|--------------|-------------|--------|----------|----------|-------------|--------------------|--------------------|--------------------|----------|----------|----------|---------------------|----------|----------------------------|-----------------------|------------------------|

| TERM.<br>NO. | NOTE 3<br>1 | 2      | 3        | 4        | NOTE 1<br>5 | NOTE 3<br><b>6</b> | 7                  | 8                  | 9        | 10       | 11       | NOTE 3<br><b>12</b> | 13       | NOTES<br>2, 3<br><b>14</b> | I <sub>IN</sub><br>mA | I <sub>OUT</sub><br>mA |

| 1<br>Note 3  |             | Note 4 | Note 4   | Note 4   | Note 4      | 15<br>0            | 10<br>-2           | Note 4             | Note 4   | Note 4   | Note 4   | Note 4              | Note 4   | Note 4                     | 10                    | 0.1                    |

| 2            |             |        | 0<br>-15 | 0<br>-15 | 2<br>-14    | 0<br>-14           | 0<br>Note 5<br>-14 | 0<br>Note 5<br>-14 | 0<br>-14 | 0<br>-14 | 0<br>-14 | Note 4              | 0<br>-14 | 0<br>-14                   | 150                   | 10                     |

| 3            |             |        |          | 0<br>-15 | Note 4      | Note 4             | Note 4             | Note 4             | Note 4   | Note 4   | Note 4   | Note 4              | Note 4   | Note 4                     | Note 4                | Note 4                 |

| 4            |             |        |          |          | Note 4      | 2<br>-10           | Note 4             | Note 4             | Note 4   | Note 4   | Note 4   | Note 4              | Note 4   | Note 4                     | 0.1                   | 150                    |

| 5<br>Note 1  |             |        |          |          |             | Note 4             | 7<br>-7            | Note 4             | Note 4   | Note 4   | Note 4   | Note 4              | Note 4   | Note 4                     | 50                    | 10                     |

| 6<br>Note 3  |             |        |          |          |             |                    | 14<br>0            | Note 4             | Note 4   | Note 4   | Note 4   | Note 4              | Note 4   | Note 4                     | Note 4                | Note 4                 |

| 7            |             |        |          |          |             |                    |                    | Note 4             | 14<br>0  | Note 4   | 20<br>0  | 2.5<br>-2.5         | 14<br>0  | 6<br>-6                    | Note 4                | Note 4                 |

| 8            |             |        |          |          |             |                    |                    |                    | 10<br>0  | Note 4   | Note 4   | Note 4              | Note 4   | Note 4                     | 0.1                   | 2                      |

| 9            |             |        |          |          |             |                    |                    |                    |          | Note 4   | Note 4   | Note 4              | Note 4   | Note 4                     | Note 4                | Note 4                 |

| 10           |             |        |          |          |             |                    |                    |                    |          |          | Note 4   | Note 4              | Note 4   | Note 4                     | Note 4                | Note4                  |

| 11           |             |        |          |          |             |                    |                    |                    |          |          |          | Note 4              | Note 4   | Note 4                     | Note 4                | Note4                  |

| 12<br>Note 3 |             |        |          |          |             |                    |                    |                    |          |          |          |                     | Note 4   | Note 4                     | 50                    | 50                     |

| 13           |             |        |          |          |             |                    |                    |                    |          |          |          |                     |          | Note 4                     | Note 4                | Note4                  |

| 14<br>Note 3 |             |        |          |          |             |                    |                    |                    |          |          |          |                     |          |                            | 2                     | 2                      |

This chart gives the range of voltages which can be applied to the terminals listed horizontally with respect to the terminals listed vertically. For example, the voltage range of horizontal Terminal 6 to vertical Terminal 4 is 2V to -10V.

NOTES:

1. Resistance should be inserted between Terminal 5 and external supply or line voltage for limiting current into Terminal 5 to less than 50mA.

2. Resistance should be inserted between Terminal 14 and external supply for limiting current into Terminal 14 to less than 2mA.

3. For the CA3079 indicated terminal is internally connected and, therefore, should not be used.

4. Voltages are not normally applied between these terminals; however, voltages appearing between these terminals are safe, if the specified voltage limits between all other terminals are not exceeded.

5. For CA3079 (0V to -10V).

**TEST CIRCUIT FOR CA3059 AND CA3079**

FIGURE 7A. GATE PULSE DURATION TEST CIRCUIT WITH ASSOCIATED WAVEFORM FOR CA3059 AND CA3079

FIGURE 7C. PULSE DURATION AFTER ZERO CROSSING vs EXTERNAL CAPACITANCE FOR CA3059 & CA3079

FIGURE 7B. TOTAL GATE PULSE DURATION vs EXTERNAL CAPACITANCE FOR CA3059 AND CA3079

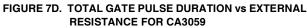

FIGURE 9. INPUT BIAS CURRENT TEST CIRCUIT FOR CA3059 AND CA3079 CA3059, CA3079

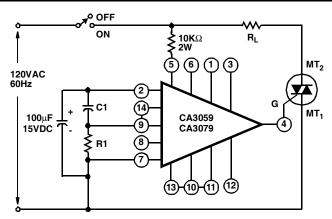

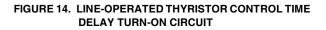

$t_{ON} = 0.67 R_1 C_1$ R<sub>1</sub>(max. value allowable) = 1m $\Omega$

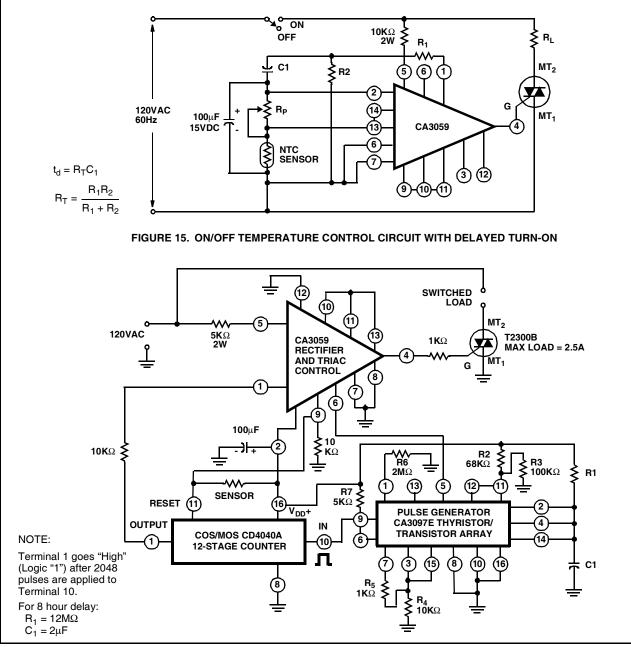

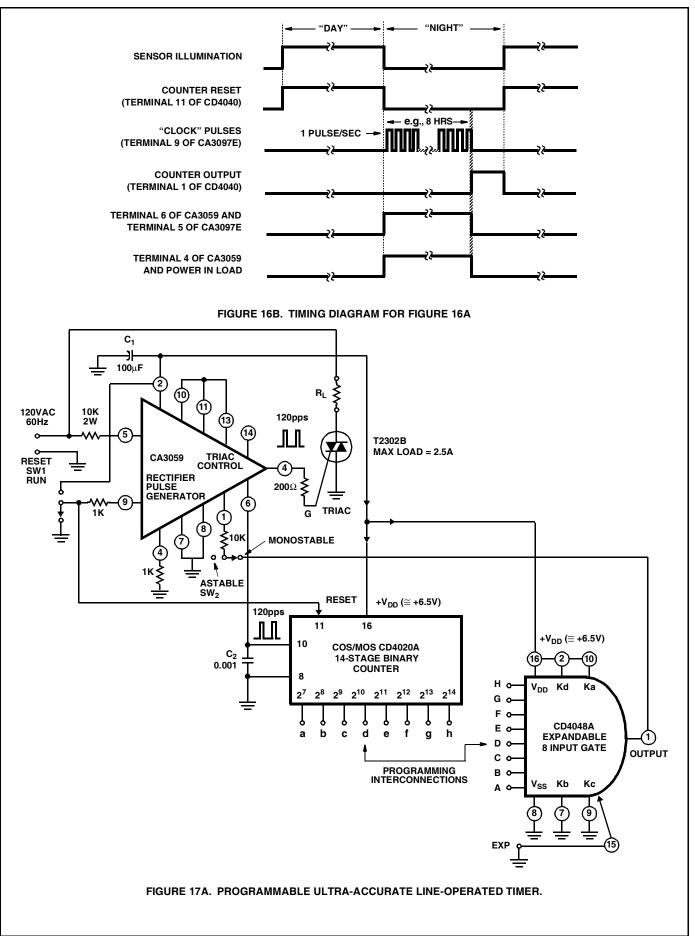

FIGURE 16A. LINE-OPERATED IC TIMER FOR LONG TIME PERIODS

# CA3059, CA3079

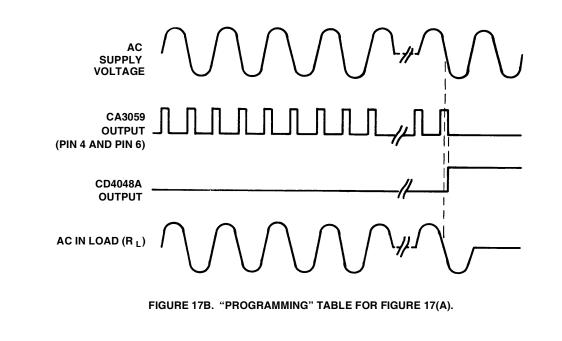

| 1t | 2t | 4t | 8t        | 16t      | 32t | 64t | 128t | to   |

|----|----|----|-----------|----------|-----|-----|------|------|

|    | -  | -  | CD4020A T | ERMINALS | -   | -   | -    |      |

| а  | b  | c  | d         | е        | f   | g   | h    |      |

|    | _  | _  | CD4048A T | ERMINALS | _   | _   | _    |      |

| Α  | В  | C  | D         | E        | F   | G   | Н    |      |

| С  | NC | NC | NC        | NC       | NC  | NC  | NC   | 11   |

| NC | С  | NC | NC        | NC       | NC  | NC  | NC   | 21   |

| С  | С  | NC | NC        | NC       | NC  | NC  | NC   | 31   |

| NC | NC | С  | NC        | NC       | NC  | NC  | NC   | 41   |

| С  | NC | С  | NC        | NC       | NC  | NC  | NC   | 51   |

| NC | С  | С  | NC        | NC       | NC  | NC  | NC   | 61   |

| С  | С  | С  | NC        | NC       | NC  | NC  | NC   | 71   |

| NC | NC | NC | С         | NC       | NC  | NC  | NC   | 81   |

| С  | NC | NC | С         | NC       | NC  | NC  | NC   | 91   |

| NC | С  | NC | С         | NC       | NC  | NC  | NC   | 101  |

| С  | С  | NC | С         | NC       | NC  | NC  | NC   | 111  |

| NC | NC | С  | С         | NC       | NC  | NC  | NC   | 121  |

| С  | NC | С  | С         | NC       | NC  | NC  | NC   | 131  |

| NC | С  | С  | С         | NC       | NC  | NC  | NC   | 141  |

| С  | С  | С  | С         | NC       | NC  | NC  | NC   | 151  |

| С  | С  | С  | С         | NC       | С   | С   | NC   | 1111 |

| NC | NC | NC | NC        | С        | С   | С   | NC   | 1121 |

| С  | NC | NC | NC        | С        | С   | С   | NC   | 113  |

| С  | с  | с  | с         | С        | С   | с   | с    | 2551 |

NOTES:

1.  $t_0 = \text{Total time delay} = n_1 t + n_2 t + \dots n_n t$ .

2. C = Connect. For example, interconnect terminal a of the CD4020A and terminal A of the CD4048A.

3. NC = No Connection. For example, terminal b of the CD4020A open and terminal B of the CD4048A connected to  $+V_{DD}$  bus.

# **Operating Considerations**

#### Power Supply Considerations for CA3059 and CA3079

The CA3059 and CA3079 are intended for operation as selfpowered circuits with the power supplied from and AC line through a dropping resistor. The internal supply is designed to allow for some current to be drawn by the auxiliary power circuits. Typical power supply characteristics are given in Figures 2(b) and 2(c).

#### **Power Supply Considerations for CA3059**

The output current available from the internal supply may not be adequate for higher power applications. In such applications an external power supply with a higher voltage should be used with a resulting increase in the output level. (See Figure 4 for the peak output current characteristics.) When an external power supply is used, Terminal 5 should be connected to Terminal 7 and the synchronizing voltage applied to Terminal 12 as illustrated in Figure 5(a).

#### **Operation of Built-In Protection for the CA3059**

A special feature of the CA3059 is the inclusion of a protection circuit which, when connected, removes power from the load if the sensor either shorts or opens. The protection circuit is activated by connecting Terminal 14 to Terminal 13 as shown in the Functional Block Diagram. To assure proper operation of the protection circuit the following conditions should be observed:

1. Use the internal supply and limit the external load current to 2mA with a  $5k\Omega$  dropping resistor.

- 2. Set the value of  $R_P$  and sensor resistance ( $R_X$ ) between  $2k\Omega$  and  $100k\Omega$ .

- 3. The ratio of R<sub>X</sub> to R<sub>P</sub>, typically, should be greater than 0.33 and less than 3. If either of these ratios is not met with an unmodified sensor over the entire anticipated temperature range, then either a series or shunt resistor must be added to avoid undesired activation of the circuit.

If operation of the protection circuit is desired under conditions other than those specified above, then apply the data given in Figure 12.

#### **External Inhibit Function for the CA3059**

A priority inhibit command may be applied to Terminal 1. The presence of at least +1.2V at 10 $\mu$ A will remove drive from the thyristor. This required level is compatible with DTL or T<sup>2</sup>L logic. A logical 1 activates the inhibit function.

#### DC Gate Current Mode for the CA3059

Connecting Terminals 7 and 12 disables the zero-crossing detector and permits the flow of gate current on demand from the differential sensing amplifier. This mode of operation is useful when comparator operation is desired or when inductive loads are switched. Care must be exercised to avoid overloading the internal power supply when operating in this mode. A sensitive gate thyristor should be used with a resistor placed between Terminal 4 and the gate in order to limit the gate current.

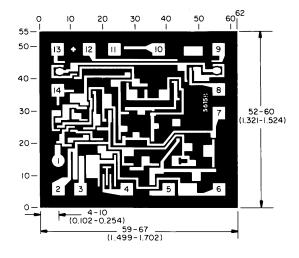

Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid gradations are in mils  $(10^{-3} \text{ inch})$ .

The photographs and dimensions represent a chip when it is par of the wafer. When the wafer is cut into chips, the cleavage angles are  $57^{\circ}$  instead of  $90^{\circ}$  with respect to the face of the chip. Therefore, the isolated chip is actually 7 mils (0.17mm) larger in both dimensions.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's guality certifications can be viewed at www.intersil.com/design/guality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time withou notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may resul from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.