## MOS DIGITAL INTEGRATED CIRCUIT $\mu$ PD1701C-011

# PHASE LOCKED LOOP FREQUENCY SYNTHESIZER LW/MW/FM DIGITAL TUNING SYSTEM CONTROLLER CMOS LSI

## DESCRIPTION

The  $\mu$ PD1701C-011 is a single chip CMOS LSI designed for using as a PLL Frequency Synthesizer Digital Tuning System Controller.

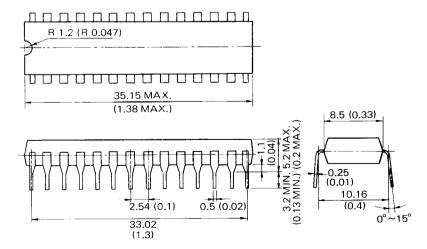

The  $\mu$ PD1701C-011 is packaged in a 28 pin slim dual in-line package (DIP).

## **FEATURES**

- Clock, PLL and Controller is realized in a single chip.

- LW, MW and FM bands for Europe

- High reference frequency (FM: 25 kHz) It results in a high carrier to noise ratio.

- External programmable IF offset for FM band (10.650 MHz, 10.675 MHz, 10.700 MHz, 10.725 MHz)

- High speed and low power consumption due to CMOS.

- Stand-by mode . . .supply current IDD = 0.5 mA (TYP.)

- Display brightness control (DIMMER)

### **FUNCTION OF RADIO**

- Automatic up search (SEEK ARI/STEREO)

- Automatic down search (SEEK ARI/STEREO)

- Manual up search

- Manual down search

- Preset station memory . . . . FM: 6 stations, MW: 6 stations

- Last station memory . . . . . FM: 1 station, MW: 1 station, LW: 1 station

## **FUNCTION OF CLOCK**

- 24 hour display format . . . . hours, minutes, colon

- Leading-zero blanking

- Hours and minutes set controls

- Minutes and seconds reset control

## PACKAGE DIMENSIONS in millimeters (inches)

NEC cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

NEC reserves the right to make changes at any time without notice in order to improve

Nippon Electric Co.,Ltd.

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage        | $V_{DD}$ | 0.3 to +6.0                           | V  |

|-----------------------|----------|---------------------------------------|----|

| Input Voltage         | VI       | $-0.3$ to $V_{\mbox{DD}}$             | V  |

| Output Voltage        | VO       | $-0.3$ to $V_{\mbox{\scriptsize DD}}$ | V  |

| Output Current        | ЮН       | -10                                   | mA |

| Storage Temperature   | Tstg     | -55 to +125                           | °C |

| Operation Temperature | Topt     | -35 to +75                            | °C |

## ELECTRICAL CHARACTERISTICS (Ta=-35 to +75 $^{\circ}$ C, V<sub>DD</sub>=4.5 to 5.5 V)

| CHARACTERISTIC            | SYMBOL           | MIN.               | TYP. | MAX.               | UNIT | TEST CONDITIONS                           |

|---------------------------|------------------|--------------------|------|--------------------|------|-------------------------------------------|

|                           | VIH1             | 0.8V <sub>DD</sub> |      | V <sub>DD</sub>    | V    | SD terminal                               |

| High Level Input Voltage  | V <sub>IH2</sub> | 0.7V <sub>DD</sub> |      | V <sub>DD</sub>    | V    | CE terminal                               |

|                           | VIH3             | 0.6V <sub>DD</sub> |      | V <sub>DD</sub>    | V    | K0 to K3 terminals.                       |

|                           | VIL1             | 0                  |      | 0.3V <sub>DD</sub> | V    | CE terminal                               |

| Low Level Input Voltage   | VIL2             | 0                  |      | 0.2V <sub>DD</sub> | V    | SD, K0 to K3 terminals.                   |

|                           | V <sub>OH1</sub> | 4.0                |      |                    | V    | EO, D, MUTE: I <sub>OH</sub> =-0.5 mA     |

| High Level Output Voltage | VOH2             | 4.0                |      |                    | V    | SEG: IOH=-1.0 mA                          |

|                           | Vонз             | 4.0                |      |                    | V    | PSC: I <sub>OH</sub> =-0.2 mA             |

|                           | VOL1             |                    |      | 0.5                | V    | EO: IOL=0.5 mA                            |

| Low Level Output Voltage  | VOL2             |                    |      | 0.5                | ٧    | D,SEG,MUTE,PSC: IOL=0.2 mA                |

| High Level Input Current  | ΙΗ               | 5.0                | 25   | 100                | μΑ   | K: V <sub>I</sub> =V <sub>DD</sub> =5.0 V |

|                           | fin1             | 0.5                |      | 2.5                | MHz  | AM: vi=1.0 Vp-p, DC cut, sine wave        |

| Frequency Response        | fin2             | 0.5                |      | 8.8                | MHz  | FM: vi=0.8 Vp-p, DC cut, square wave      |

| Supply Voltage Rise Time  | Tr               |                    |      | 0.5                | s    | V <sub>DD</sub> : 0 → 4.5 V               |

| Supply Current            | 1DD              |                    | 0.5  | 2.0                | mA   | CE: Low Level                             |

#### SYSTEM DESCRIPTION

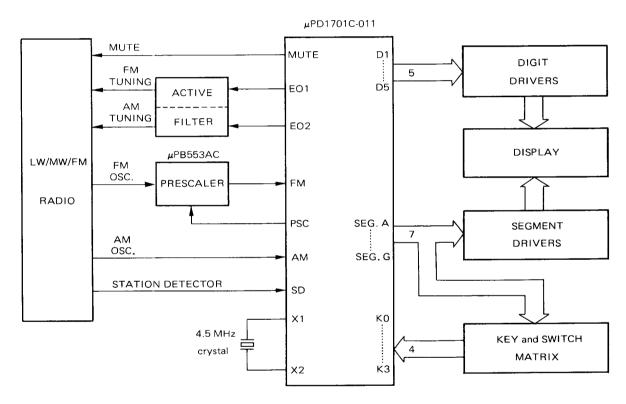

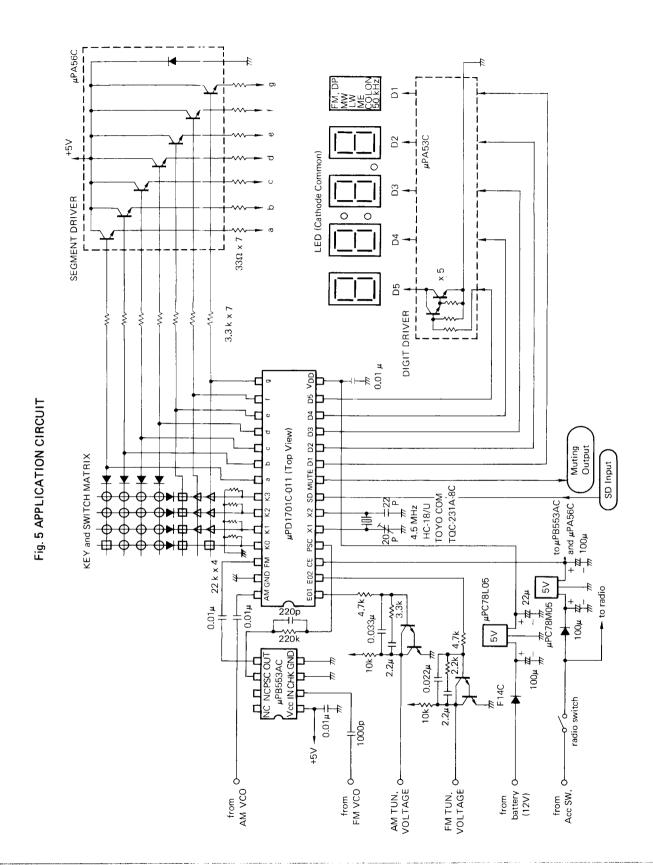

NEC's Digital Tuning System provides full electronic control of a vari-cap tuned FM/AM radio receiver and stereo. The block diagram of the system is shown in Fig. 1. This is a Phase Locked Loop Digital Tuning System which consists of two integrated circuits; controller plus PLL in a single chip, and two-modulus prescaler.

The controller (µPD1761C-011) provides Phase Locked Loop capability with on-chip frequency division, a reference oscillator whose frequency is controlled by an external crystal of 4.5 MHz, and phase comparator circuitry. It accepts directly an AM local oscillator signal and an FM signal from two-modulus prescaler (µPB553AC), and outputs control signals for closed loop operation of these oscillators. The outputs drives filters for supplying analog voltages to the vari-cap tuners. The controller also provides the signals to drive the display. The frequency of the tuned station is displayed on a 3.5 digit multiplexed display. Six favorite stations on each band can be stored as well as "last stations tuned" information.

The two-modulus prescaler (µPB553AC) is suitable for pulse swallowing in this system.

Fig. 1 BLOCK DIAGRAM

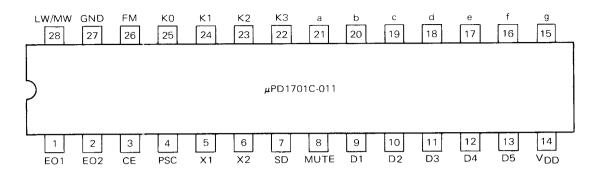

## PIN CONNECTION (Top View)

## **EXPLANATION OF INPUT AND OUTPUT TERMINALS**

| EO1<br>EO2      | These three-state outputs are used (via active filters) to supply analog voltages to the tuner vari-cap for controlling the local osc.                   |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE              | This input is used to designate the stand-by mode to the chip. It is low to designate the stand-by mode. (Display: off, PLL: disabled)                   |

| PSC             | This output is used to control the division ratio of the FM two-modulus prescaler ( $\mu$ PB553AC).                                                      |

| X1, X2          | These inputs are for connection to a 4.5 MHz crystal.                                                                                                    |

| SD              | This input is used to control the station searching operation (AU/AD). It is high to indicate the presence of a station and the operation is terminated. |

| MUTE            | This output line is high to mute the radio in the case of station change, band change, and so on.                                                        |

| D1 to D5        | These outputs are used as digit drivers for the display.                                                                                                 |

| V <sub>DD</sub> | This is a 4.5 to 5.5 volt supply for the chip.                                                                                                           |

| a to g          | These outputs are used as segment drivers for the display. They are also used as vertical drive for the control key and mode switch matrix.              |

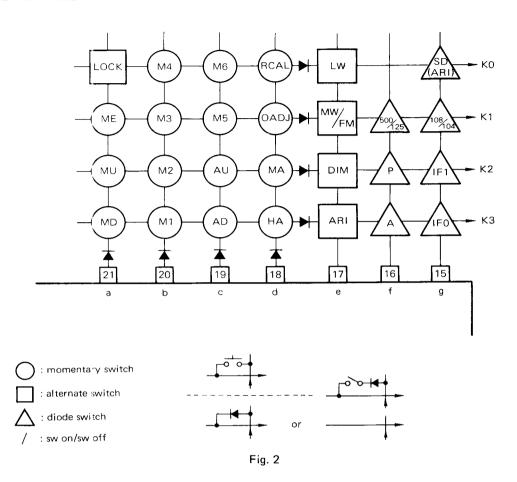

| K0 to K3        | These inputs are from seven by four matrix. Various functions are entered through the matrix. See Fig. 2 for the matrix assignments.                     |

| FM              | This is the FM band local oscillator input. The frequency is divided by 16/17 using a two-modulus prescaler (µPB553AC).                                  |

| GND             | System ground.                                                                                                                                           |

| LW/MW           | This input is the LW/MW band local oscillator input.                                                                                                     |

## CONTROL KEY AND MODE SWITCH MATRIX

## \* Manual up or down search

MU, MD A momentary depression will tune to next channel, and continuous depression more than 0.5 second allows traversing up or down the entire band until the key is released.

## \* Automatic up or down search

AU, AD A momentary depression causes automatic up or down search which is terminated by activation (SEEK) of SD terminal (active high).

## \* Preset of the station

ME The tuning information is stored into internal RAM by depressing ME key and then the desired memory key within 5 seconds from the time ME key was initially depressed. If any key is depressed in this period, the ME function is cancelled.

M1 to M6 Six favorite stations can be recalled from internal RAM for each band. When it is switched from one band to another band, it will tune to "last-tuned-to station" on that band. Each time a station is changed, the controller provides a signal to mute the radio.

#### \* Clock function

Ρ

HA, MA These keys are used for hours and minutes setting. (See note)

OADJ A momentary depression resets minutes and seconds.

NOTE: MU and MD keys can be used to set minutes and hours, keeping depressing ME key when time is displayed.

#### Switching-over the display

RCAL A momentary depression will change the display mode when radio is on.

A ON: Frequency is given priority for the display.

OFF: Clock is given priority for the display.

ON: There is a priority on the display.

When RCAL key depressed, the display returns to the prior matter after 5 sec display of

another.

OFF: There is no priority on the display.

DIMMER ON: Display brightness is reduced (duty: 20 % of normal brightness).

OFF: Display brightness is normal.

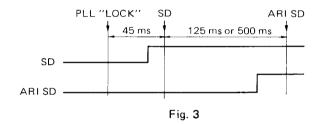

## \* ARI/STEREO search

ARI OFF: Normal automatic search (AU, AD)

ON: In the case of FM band, ARI/STEREO search is possible.

A momentary depression of AU/AD key causes up or down ARI/STEREO search which is terminated by activation of SD terminal and ARI SD switch. (Timing diagram is shown

below.)

500/125 This switch is for a selection of timing in the case of ARI/STEREO search.

ON: The controller waits 500 ms from the activation of SD terminal.

OFF: The controller waits 125 ms from the activation of SD terminal.

ARTSD This switch is normally a transistor switch. In the case of ART/STEREO search, ART (SK, BK or

DK) or STEREO SD signal is read from this switch.

## \* Selection of the radio band

LW, MW/FM

These switches are for selection of the radio band (LW, MW, FM).

| LW  | MW/FM | BAND | Receiving Frequency  | Channel<br>Spacing | Intermediate<br>Frequency |

|-----|-------|------|----------------------|--------------------|---------------------------|

| ON  | ×     | LW   | 155 to 281 kHz       | 9 kHz              | 450 kHz                   |

| OFF | ON    | MW   | 531 to 1602 kHz      | 9 kHz              | 450 kHz                   |

| OFF | OFF   | FM   | 87.5 to 104/108 MHz* | 50 kHz             | **                        |

x : Don't care.

Table 1

IFO, IF1\*\* Two external diodes program the chip to accept 4 different frequencies from 10.650 MHz to 10.725 MHz in 25 kHz steps.

| IF0 | IF1 | Intermediate Frequency |

|-----|-----|------------------------|

| OFF | ON  | 10.650 MHz             |

| ON  | ON  | 10.675 MHz             |

| OFF | OFF | 10.700 MHz             |

| ON  | OFF | 10.725 MHz             |

Table 2

108/104\* This switch is used to preset the FM receiving band.

| 108/104 | Receiving Frequency     |

|---------|-------------------------|

| ON      | 87.50 MHz to 108.00 MHz |

| OFF     | 87.50 MHz to 104.00 MHz |

Table 3

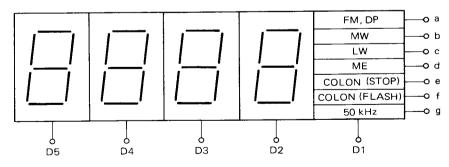

## \* Display interface

The center frequency of tuned station is displayed on a 3.5 digit LED display. The segment outputs a, b, c, d, e, f, and g are also used as inputs for 7 segment drivers. The segment output go to common collector NPN transistor array ( $\mu$ PA56C) to drive the segments of the common cathode 7 segment LED display. The digit outputs go to NPN darlington transistor array ( $\mu$ PA53C) to drive the LED display.

Fig. 4

Nippon Electric Co.,Ltd.

IC = 1271 MAR. = 22 = 80RK Printed in Japan

NEC Building, 33-1, Shiba Gochome, Minato-ku, Tokyo 108, Japan Tel.: Tokyo 454-1111

Telex Address: NECTOK J22686

Cable Address: MICROPHONE TOKYO

013895 X - X